小さなCPUに数百億個の極小トランジスタを詰め込む製造装置「EUVリソグラフィ」は一体どんな仕組みなのか?

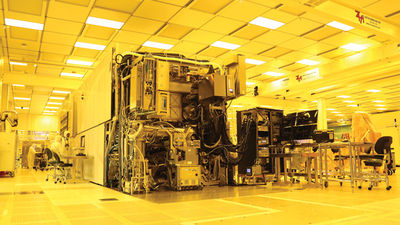

ノートPCやスマートフォン、AIサーバーなど、既存のハイテク機器の内部には最先端の半導体が組み込まれています。この中には数百億個ものトランジスタが詰め込まれており、そのサイズは最小10nmほどと極小です。そんな超極小のトランジスタを製造するのに欠かせないテクノロジーのひとつが「極端紫外線(EUV)リソグラフィ」で、その仕組みをBranch Educationが解説しています。

How are Billions of Nanoscopic Transistors Made into a Microchip? EUV Photolithography 🛠⚙️🤯 - YouTube

Branch EducationはEUVリソグラフィを「ナノスケールのコピー機」と表現しています。そんなEUVリソグラフィの動作を簡単に説明すると以下の通り。

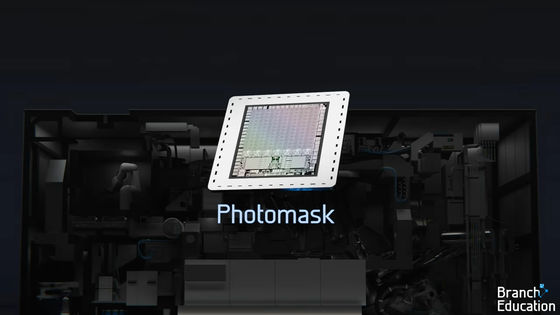

1:チップ一層分の設計データをフォトマスクと呼ばれる板に記録。

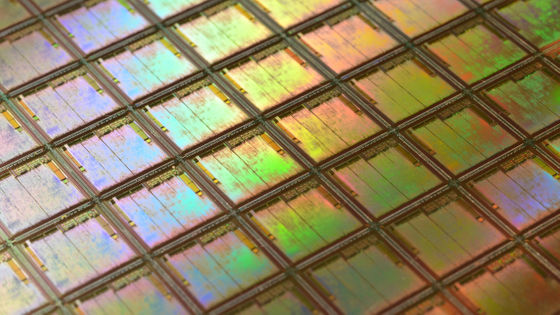

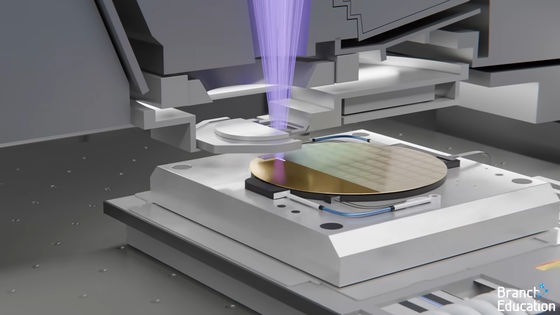

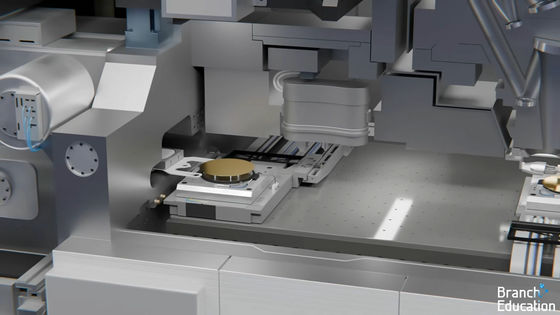

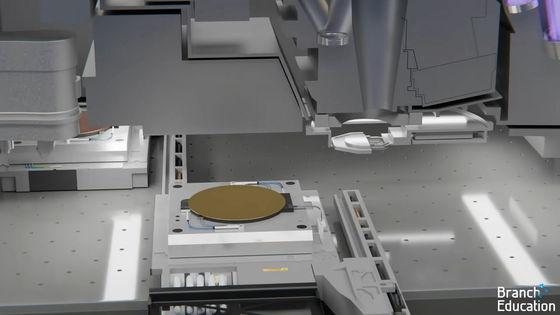

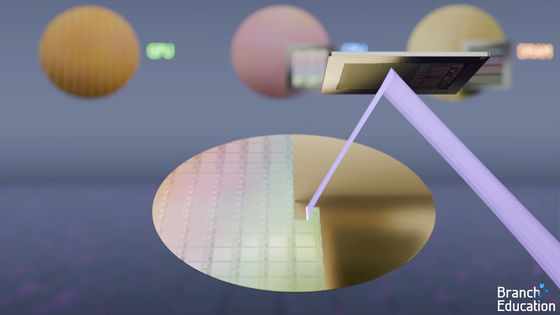

2:300mmのシリコンウェハー(前処理済み)を装置内にセット。

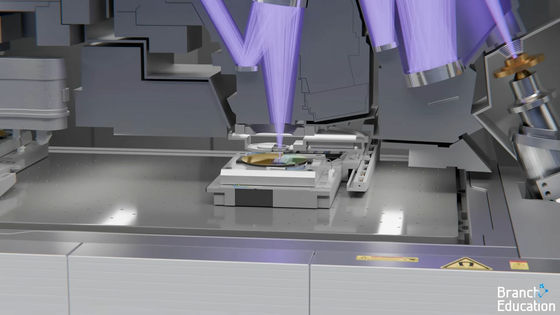

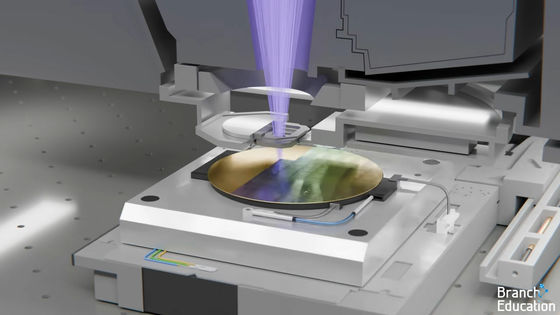

3:装置は極端紫外線(EUV)光と鏡の組み合わせを使って、フォトマスク上の設計をウェハーに転写。

4:ウェハーを少しずつ動かしながら同じパターンを何度もコピー。

5:1枚のウェハーに100個以上のマイクロチップが転写されると、次のウェハーを投入。

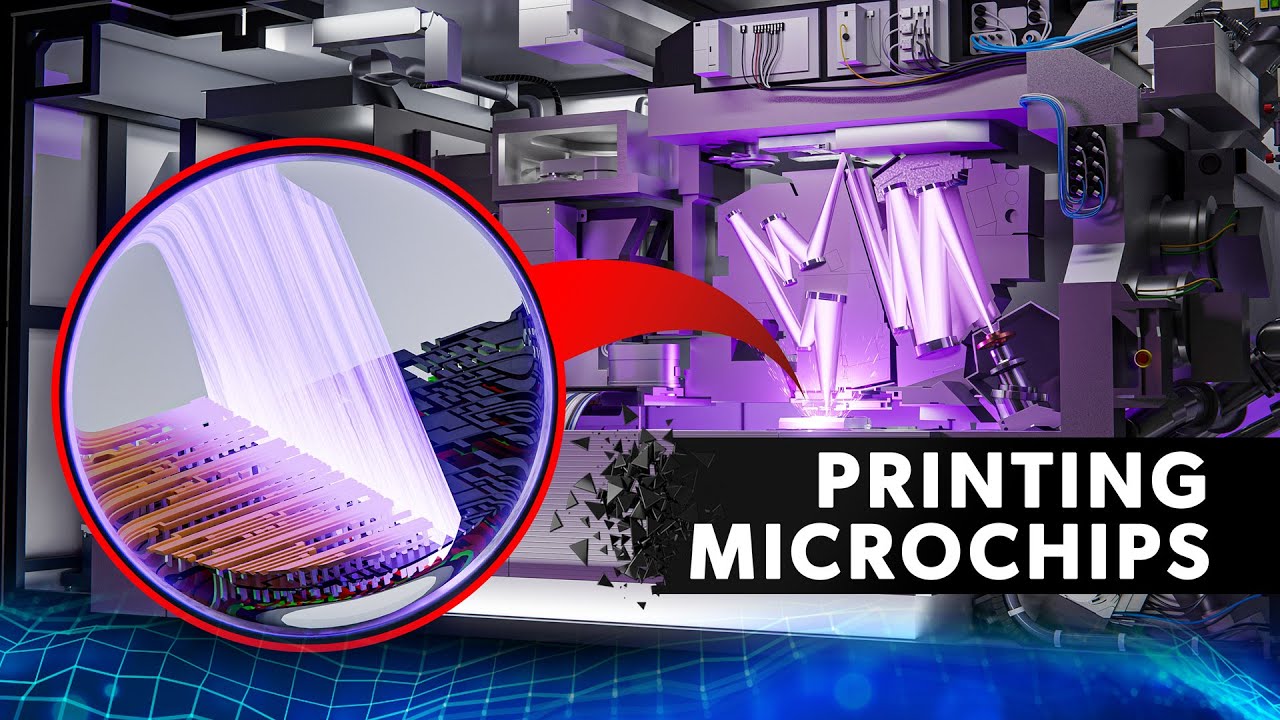

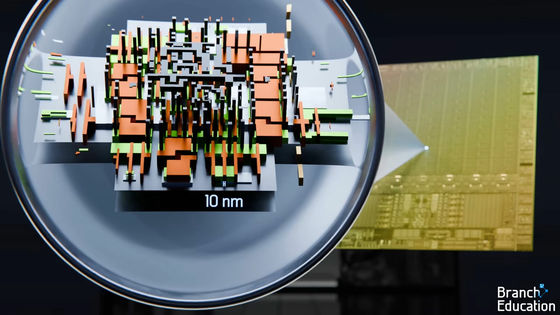

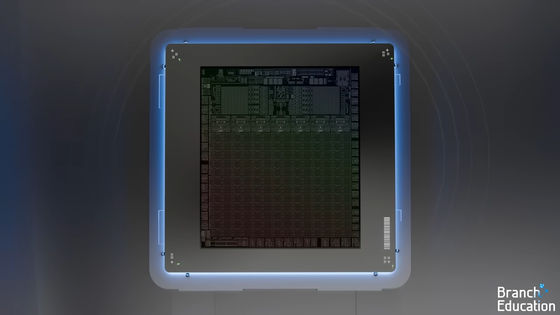

EUVリソグラフィは約18秒で1枚のウェハー上に同じチップを約100回コピーします。例えばGPUの場合、約300億個のトランジスタが含まれていますが、ナノスケールで見ると、何層にも重なる配線とトランジスタが3次元的に構成されており、最も小さな部分は10nmしかありません。

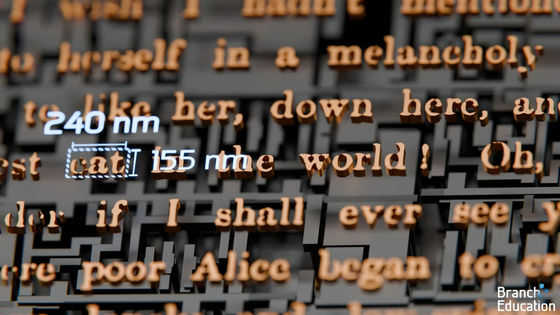

EUVリソグラフィは最下層の微細なパターンを形成する際に使用され、上層部の比較的大きなパターンには別の露光装置が使われるそうです。EUVリソグラフィが文字を印刷できると仮定すると、1本の線の幅は13nmであるため、単語で「Cat」と書いてもサイズはわずか「155×240nm」程度になります。EUVリソグラフィを使って文章を書くと、小説1ページ分の文章を印刷してもサイズは赤血球ほどの大きさにしかなりません。

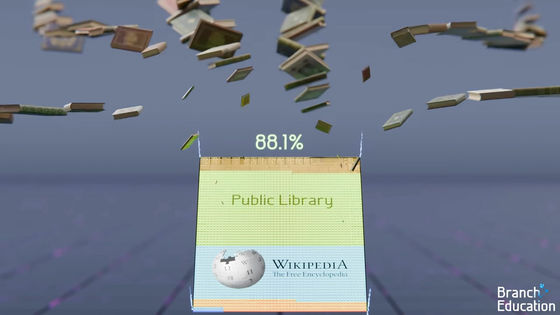

通常のGPUチップと同程度の面積を使えば、図書館の全蔵書を余裕で印刷できます。そして、EUVリソグラフィはこの膨大な量の情報をわずか1秒未満でコピーすることができます。そのため、Branch Educationは「現代のあらゆるテクノロジーは、この装置によって実現していると言っても過言ではありません」と言及しました。

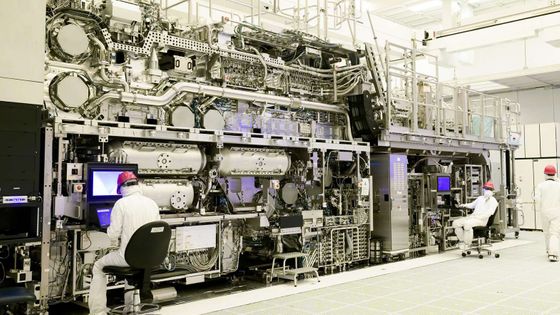

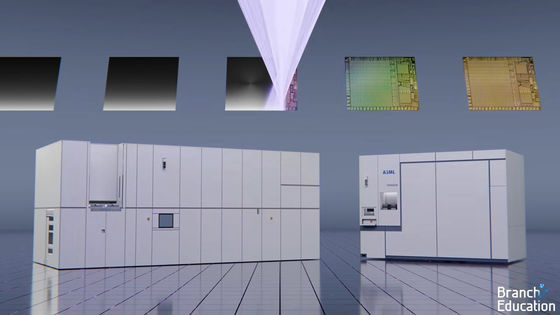

そんなEUVリソグラフィでは、まず極端紫外線光を生成するところから始まります。極端紫外線とは波長13.5nm(可視光の約1/15)の光で、これほど短波長の光は作り出すこと自体が技術的に極めて難しい課題でした。EUVリソグラフィの製造メーカーであるASMLは、液体のスズをレーザーで蒸発させることでプラズマを発生させ、その光を利用しているそうです。

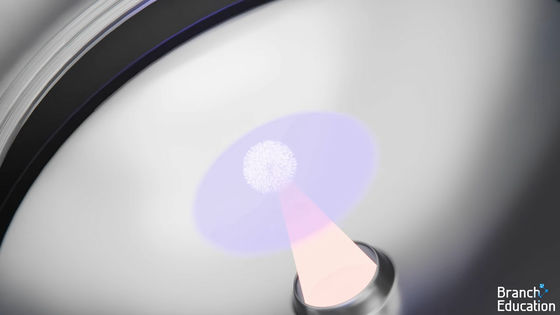

ASML製EUVリソグラフィが極端紫外線を発生させる手順は以下の通りです。簡単に言えば「液体のスズにレーザーを撃ち込み、発光するプラズマを作る」というもので、この工程は毎秒5万回以上の速度で繰り返されています。

1:スズの微小な液滴(直径約25マイクロメートル)を真空中に高速で噴射。

2:レーザーパルスを当てて液滴を扁平化。

3:強力なレーザーパルスを命中させ、液滴を約22万度のプラズマ状態に変化させます。

4:このプラズマがEUV光(紫色)を放出します。

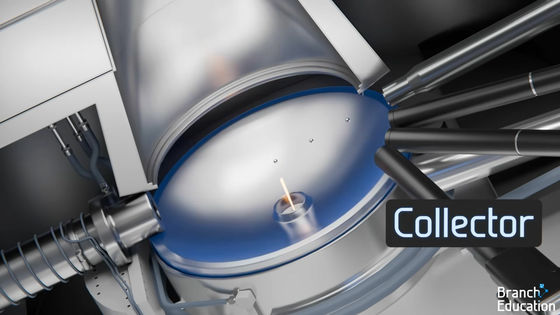

生成されたEUV光はあらゆる方向に放射されるため、効率的に集める必要があります。ここで登場するのが集光ミラー(青色部分)です。集光ミラーはEUV光を装置の次の光学モジュールに導くよう設計されているのですが、EUV光は空気中ですぐ吸収されてしまうため、装置全体が完全な真空環境の中で動作するように設計されています。なお、わずかでも酸素や窒素が混ざるとEUV光は消えてしまうそうです。

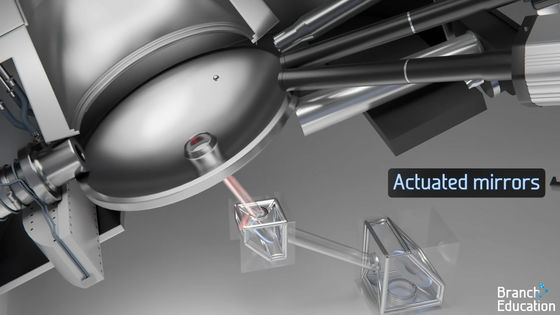

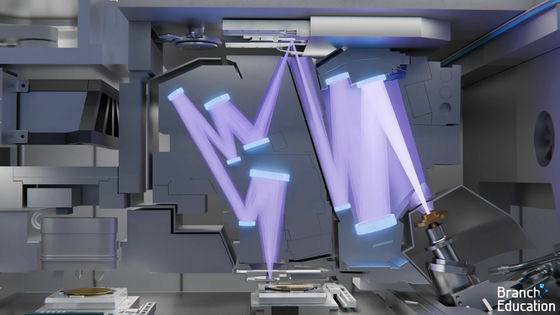

EUV光を屈折させるレンズは存在しません。なぜなら、どんなガラスもEUVを透過できないからです。そのため、EUVリソグラフィではすべて鏡で光を反射・制御しており、ASML製EUVリソグラフィではカールツァイスが開発した高精度ミラーが使用されています。

このミラーは、モリブデンとシリコンの薄膜を交互に100層以上重ねた構造となっており、反射率は約70%です。そのため、7枚の鏡を反射させるとEUV光の強度は半分以下となってしまいます。

ミラーで集めたEUV光は、照明光学系に入ります。ここで光の形状や均一性が整えられ、フォトマスク上に正確に照射されるよう制御されるわけです。フォトマスクにはチップ一層分の回路パターンが描かれており、EUVでは透過型ではなく反射型のフォトマスクが採用されます。フォトマスク表面には反射する部分と吸収する部分があり、光が反射してチップの設計が転写されるわけです。

フォトマスクの回路パターンは何百回も転写されるため、少しでも欠陥があるとウェハー上に欠陥が数百回コピーされてしまいます。そのため、ウェハーの表面精度は原子レベルで検査されることとなり、欠陥検出には電子ビームスキャナーや干渉計が使われるそうです。

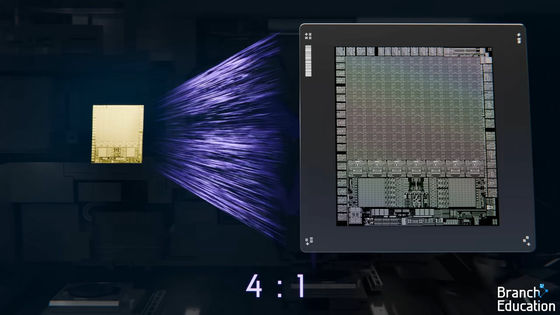

フォトマスクで反射されたEUV光は、投影光学系を通して縮小され、シリコンウェハーに投影されます。投影倍率は4分の1程度です。マスク上で1mmのパターンは、ウェハー上では0.25mmに縮小されます。この縮小を可能にしているのが、カールツァイス製の6枚の高精度ミラー群です。これらのミラーは1枚当たりの表面誤差が原子数個分しかなく、nm単位で形状が調整されています。

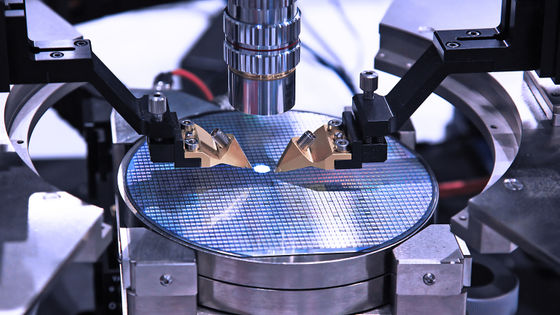

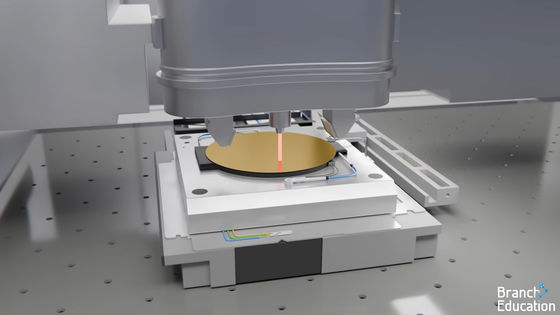

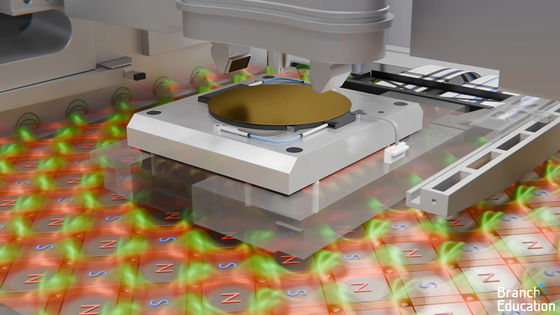

EUVリソグラフィの中で最も驚異的な機構のひとつがウェハーステージです。これは300nmのシリコンウェハーを1nm以下の精度で位置決めしながら、高速で動かすものとなっています。露光中、ウェハーステージは常に加速・減速を繰り返します。しかも、露光のたびに次のショット位置にわずか数ミリ秒で移動しなければいけません。そのため、ウェハーステージの移動精度には、髪の毛の太さの10万分の1以下が求められます。

この精度を実現するため、ウェハーステージはリニアモーター方式で動作し、摩擦を完全になくすためにエアーベアリング構造を採用しています。また、ウェハーステージは光干渉計によって常にモニタリングされながら、nm単位で位置を補正しながら露光を行うため、マスクステージとウェハーステージは完全に同期して動作しなければいけません。

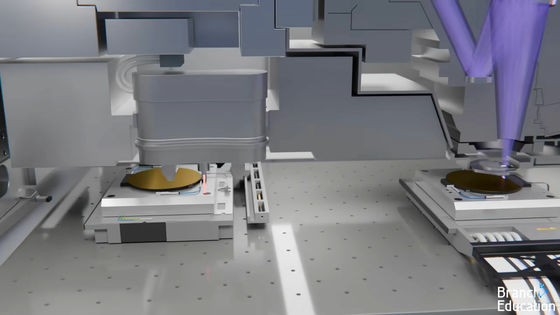

これを実現しているのは、ASMLが独自開発したTwinScanです。TwinScanでは「一方のステージで露光を行いながら、もう一方のステージで次のウェハーを測定・準備する」という並列動作を実現しています。このおかげで処理速度は飛躍的に向上しているそうです。

EUV光は空気中で消えてしまうため、露光工程全体が高真空チャンバー内で行われます。しかし、チャンバー内ではスズの残留粒子や鏡面の汚染が発生するため、ASML製EUVリソグラフィにはスズ粒子を除去する磁場フィルターやミラー洗浄レーザーが内蔵されているそうです。このメンテナンス機構がなければ、鏡の反射率はわずか数日で低下してしまう模様。

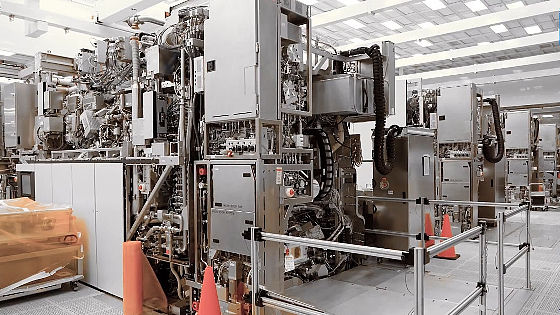

EUVリソグラフィは、実質的に「ナノスケール精度の巨大ロボット」です。1台当たり10万個以上のセンサーを搭載しており、それらがリアルタイムでフィードバック制御を行います。各モジュール間では光学・熱・機械的なパラメータが連動しており、これらを統合制御するため数百のCPUとFPGA、専用AIチップが使われています。EUVリソグラフィメーカーのASMLによれば、EUV露光1回あたりの制御データ量は100GBを超えており、1台の露光機で小さなデータセンター並みの処理をリアルタイムで行うそうです。

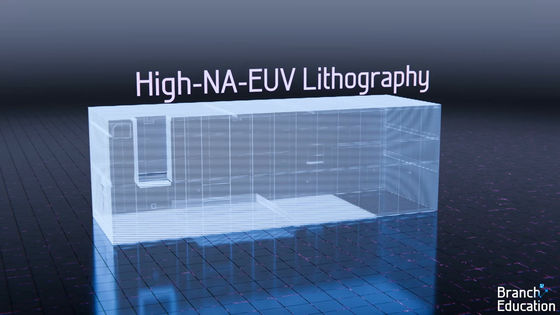

記事作成時点でのEUVリソグラフィは、3nm世代から2nm世代のチップ製造を主流としています。しかし、トランジスタがさらに微細化し、1.4nmや1nm世代へ進むと、EUVの波長13.5nmでは物理的な限界が近づいてきます。そのため、次のステップとして注目されているのがHigh NA EUV(高開口数EUV)です。光学倍率を上げ、解像度をさらに高める方式となっており、EUV二重露光やナノインプリント技術との併用となっています。将来に向け、ソフトX線リソグラフィや電子ビーム直描などの研究も進行中です。

・関連記事

ロシアがASMLに対抗するべく独自のEUV露光装置を開発開始 - GIGAZINE

ASMLとTSMCは中国の台湾侵攻に備えて半導体製造装置に「リモートで無効化する機能」を搭載しているとの指摘 - GIGAZINE

Intel史上最も驚異的なマシン「EUVシステム」の裏側を追ったムービーが公開中 - GIGAZINE

IBMが5nmプロセスのチップ製造に成功、世界初のEUVリソグラフィ実用化へ - GIGAZINE

「ムーアの法則」の限界を回避できる期待の製造技術「EUVリソグラフィ」とは? - GIGAZINE

・関連コンテンツ

in 動画, Posted by logu_ii

You can read the machine translated English article What exactly is the mechanism behind 'EU….